데이터 조작

컴퓨터 구조

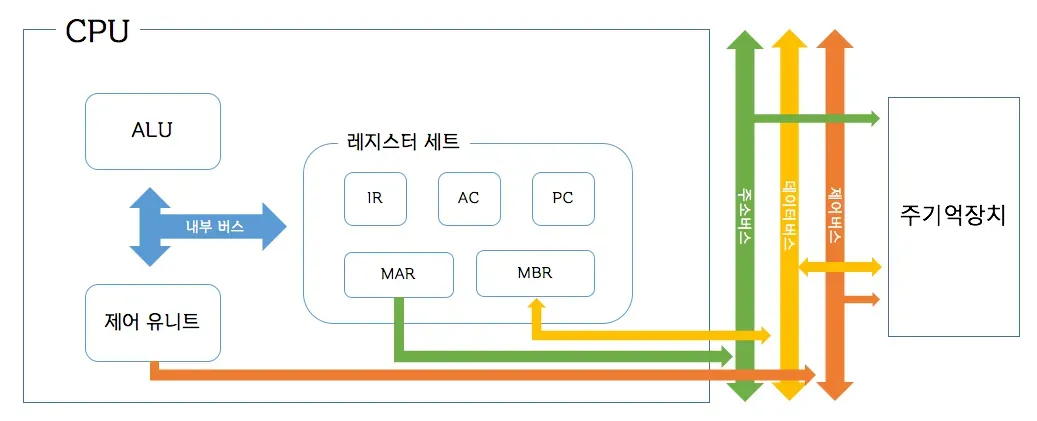

중앙처리장치 (CPU - Central Processing Unit)

- 컴퓨터의 작업을 처리하고 관리하는 중심적인 역할을 수행하는 장치

- 주요 구성 요소:

- 산술논리연산장치 (ALU - Arithmetic Logic Unit): 산술 연산(덧셈, 뺄셈 등)과 논리 연산(AND, OR, NOT 등) 수행

- 제어장치 (Control Unit): 프로그램 명령어를 해석하고 컴퓨터의 다른 부분에 제어 신호를 보내 작업을 지시

- 레지스터 (Registers): CPU 내부에 있는 고속 임시 저장 공간

레지스터 (Registers)

- CPU가 데이터를 처리하기 위해 사용하는 작은 크기의 고속 메모리

- 종류:

- 범용 레지스터 (General-Purpose Registers): 다양한 목적으로 사용될 수 있는 레지스터 (데이터 임시 저장 등)

- 용도 지정 레지스터 (Special-Purpose Registers): 특정 기능 수행을 위해 지정된 레지스터

- 명령 레지스터 (IR - Instruction Register): 현재 실행 중인 명령어를 저장

- 프로그램 카운터 (PC - Program Counter): 다음에 실행할 명령어의 메모리 주소를 저장

- 메모리 주소 레지스터 (MAR - Memory Address Register): 접근할 메모리 주소를 저장

- 메모리 버퍼 레지스터 (MBR - Memory Buffer Register): 메모리와 주고받을 데이터를 임시 저장

버스 (Bus)

- 컴퓨터 내부의 구성 요소들(CPU, 메모리, 입출력 장치 등) 간에 데이터와 신호를 전송하는 통로(전선 묶음)

- 종류:

- 데이터 버스 (Data Bus): 실제 데이터 전송 통로

- 주소 버스 (Address Bus): 데이터가 저장된 메모리 위치나 입출력 장치를 지정하는 주소 정보 전송 통로

- 제어 버스 (Control Bus): CPU의 제어 신호(읽기/쓰기 등) 및 상태 정보 전송 통로

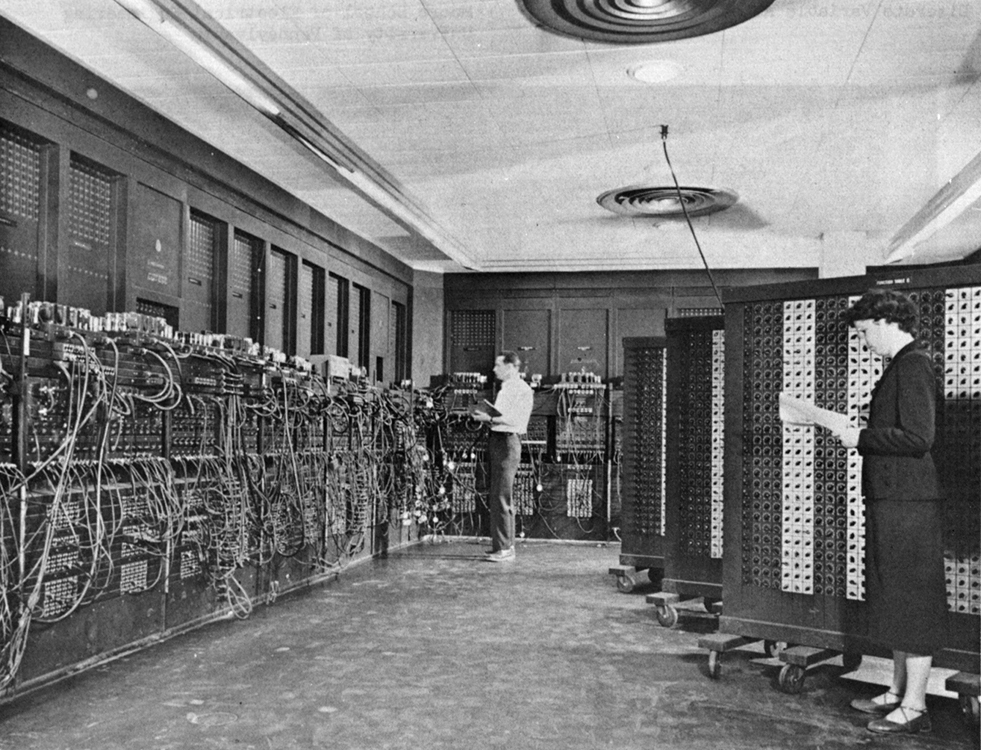

프로그램 내장 개념 (Stored-Program Concept)

- 컴퓨터 프로그램과 데이터를 주기억장치(메모리)에 저장하고, CPU가 순차적으로 명령어를 가져와 해석하고 실행하는 방식

💡

이전에는 프로그램 변경 시 물리적인 회로 변경이 필요했으나, 이 개념 도입으로 메모리 내용 변경만으로 프로그램 변경 가능

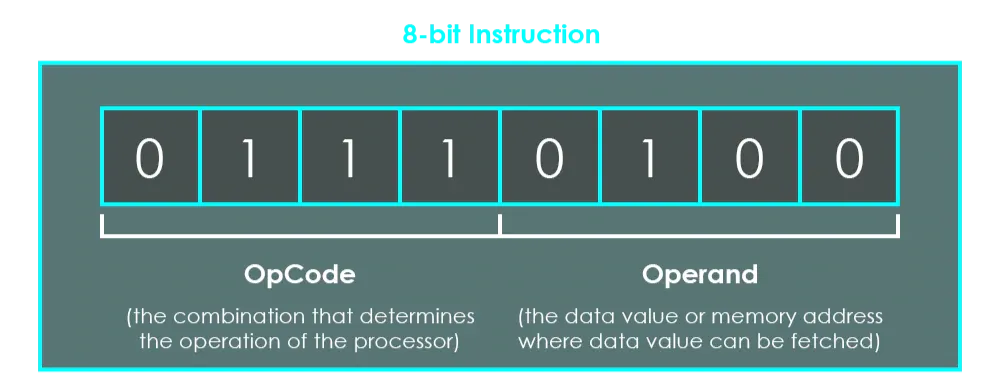

기계어

기계어 기본 (Basics)

- CPU가 인식할 수 있는 비트 패턴(0과 1)으로 인코딩된 명령어의 집합

- 기계 명령어 (Machine Instruction): 개별 동작을 지시하는 단위

- 구성:

- 연산 코드 (Opcode - Operation Code): 수행할 연산의 종류 (예: LOAD, STORE, ADD)를 나타내는 부분

- 피연산자 (Operand): 연산에 사용될 데이터나 데이터의 위치(주소, 레지스터 번호 등)를 나타내는 부분

RISC vs CISC

- CPU 명령어 집합 구조 설계 방식

- RISC (Reduced Instruction Set Computer):

- 명령어 수를 줄이고, 구조를 단순화하여 각 명령어가 한 클럭 사이클 내에 실행되도록 설계

- 고정 길이 명령어, 레지스터 기반 연산 많음

- 하드웨어 구현이 단순하지만 컴파일러 역할이 중요

- 예: PowerPC, ARM, MIPS

- CISC (Complex Instruction Set Computer):

- 다양하고 복잡한 기능을 가진 명령어를 많이 포함하여 설계

- 가변 길이 명령어, 메모리 접근 명령어 많음

- 하드웨어 구현이 복잡하지만 적은 수의 명령으로 프로그램 작성 가능

- 마이크로 코드 사용

- 예: Intel x86, AMD64

명령어의 종류 (Instruction Categories)

- 데이터 전송 (Data Transfer): 데이터를 한 위치에서 다른 위치로 이동

- CPU 레지스터와 주기억장치 간: LOAD(메모리 → 레지스터), STORE(레지스터 → 메모리)

- 데이터 이동 명령어는 일반적으로는 복사 동작이며 원본 데이터는 유지됨

- CPU 레지스터와 입출력 장치 간: IN, OUT

- 연산 (Arithmetic/Logic): 산술/논리 연산 수행을 요청.

- 산술 연산: ADD, MUL, DIV 등

- 논리 연산: AND, OR, XOR, NOT 등

- 자리 이동/회전: SHIFT, ROTATE

- 제어 (Control): 프로그램의 실행 흐름을 제어.

- 무조건 분기: JUMP

- 조건 분기: 조건에 따라 JUMP 수행 (예: JUMPEQ - 같으면 점프)

- 프로그램 종료: HALT, STOP

Vole (가상 기계어 예시)

- 학습 목적의 가상 컴퓨터 아키텍처

- 16개의 범용 레지스터 (R0 ~ RF, 16진수 표기)

- 256개의 주기억장치 셀 (주소 00 ~ FF, 16진수 표기), 각 셀은 8비트

- 명령어 형식: 16비트

- 명령 코드(Op-code): 4비트 (어떤 명령인지 지정)

- 피연산자(Operand): 12비트 (명령 수행에 필요한 추가 정보 - 레지스터 번호, 메모리 주소 등)

- 예시:

35A7(16진수)3: STORE 명령 코드5: 데이터를 가져올 레지스터 번호 (R5)A7: 데이터를 저장할 메모리 주소- 해석: "레지스터 5의 내용을 메모리 주소 A7에 저장하라."

- *16진수 사용은 긴 이진수(0011 0101 1010 0111) 표현을 간결하게 함

- 메모리 크기 관련성:

- Vole 명령어에서 메모리 주소를 표현하는 데 8비트(피연산자 일부)를 사용

- 따라서 $2^8 = 256$ 개의 서로 다른 메모리 셀을 지정 가능 (주소 0 ~ 255)

- *주소 지정 비트 수에 맞춰 메모리 크기를 설계하는 것이 효율적

프로그램 실행

프로그램 실행 과정 (Execution Process)

- 컴퓨터는 필요한 프로그램 코드나 데이터를 주기억장치에서 CPU로 복사하여 처리.

- 소스 코드 → 컴파일러 → 오브젝트 파일 → 링커 → 실행 파일 → 로더 → 메모리 적재 → CPU 실행

- ELF (Executable and Linkable Format): Unix/Linux 표준 실행 파일 형식.

- PE (Portable Executable): Windows 표준 실행 파일 형식

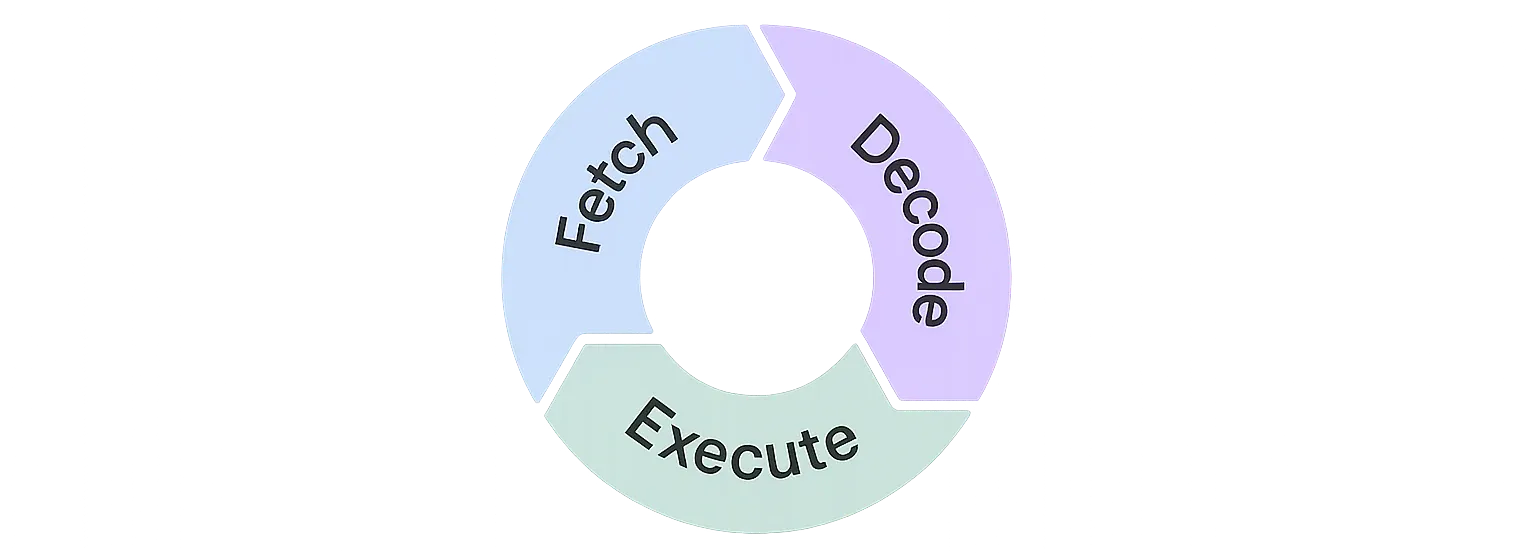

기계 주기 (Machine Cycle) 또는 CPU 주기

- CPU가 하나의 명령어를 처리하는 과정으로, 계속 반복됨

- 기계 주기는 3단계로 이루어진다:

- 인출 (Fetch):

- 프로그램 카운터(PC)가 가리키는 주기억장치 주소에서 명령어를 읽어옴

- 읽어온 명령어를 명령 레지스터(IR)에 저장

- PC 값을 다음 명령어 주소로 증가시킴 (Vole의 경우 명령어 길이가 2바이트이므로 +2)

- 해석 (Decode):

- 명령 레지스터(IR)에 있는 명령어의 연산 코드(Opcode)를 해석하여 수행할 작업을 결정

- 피연산자(Operand)를 분석하여 필요한 데이터나 주소를 파악

- 실행 (Execute):

- 해석된 명령에 따라 제어장치가 필요한 장치(ALU, 레지스터, 메모리 등)에 제어 신호를 보내 실제 연산이나 데이터 이동 등을 수행

- 인출 (Fetch):

명령어 형식이나 종류에 따라 세부 단계는 추가될 수 있다

프로그램과 데이터 구분 문제 (Program vs. Data Distinction)

- 주기억장치에는 프로그램 명령어와 데이터가 모두 0과 1의 비트 패턴으로 저장됨

- CPU 자체는 메모리의 특정 위치에 있는 비트 패턴이 명령어인지 데이터인지 구분할 방법이 없음

🚨

만약 프로그램 카운터가 데이터가 저장된 주소를 가리키게 되면, CPU는 해당 데이터를 명령어로 잘못 해석하여 실행하려 시도하며 오류 발생 가능

연산 명령

논리 연산 (Logical Operations)

- 비트 단위로 수행되는 연산

- AND: 두 비트가 모두 1일 때만 결과가 1

- 용도: 마스킹 (Masking) - 특정 비트들을 0으로 만듦 (원하는 부분만 남김)

- OR: 두 비트 중 하나라도 1이면 결과가 1

- 용도: 특정 비트들을 1로 설정

- XOR (Exclusive OR): 두 비트가 서로 다를 때만 결과가 1

- 용도: 특정 비트들을 반전, 비트 열의 보수 생성 (모든 비트가 1인 마스크와 XOR 연산)

회전 및 자리 이동 연산 (Shift and Rotate Operations)

- 레지스터 내의 비트들을 왼쪽 또는 오른쪽으로 이동시키는 연산

- 회전 (Rotate): 밀려 나가는 비트가 반대쪽 끝의 빈자리로 들어옴 (ROTATER, ROTATEL)

- 논리적 자리 이동 (Logical Shift): 밀려 나가는 비트는 버려지고, 빈자리는 0으로 채워짐 (SHIFTR, SHIFTL)

- 산술적 자리 이동 (Arithmetic Shift):

- 부호 비트를 유지하면서 이동

- 왼쪽 이동: 2의 보수 표현에서 곱하기 2 효과 (오버플로우 주의) 빈자리는 0으로 채움

- 오른쪽 이동: 2의 보수 표현에서 나누기 2 효과 (소수점 이하 버림) 빈자리는 부호 비트와 같은 값으로 채움

- 10진수에서 자릿수 이동이 곱하기/나누기 10 효과와 유사

산술 연산 (Arithmetic Operations)

- 덧셈(ADD), 뺄셈(SUB), 곱셈(MUL), 나눗셈(DIV) 등 수학적 계산 수행

입출력 장치와의 통신

제어기 (Controller) 또는 어댑터 (Adapter)

- CPU(컴퓨터 핵심 요소)와 개별 입출력 장치(프린터, 디스크 등) 사이의 중개 역할

- 메인보드 또는 별도 카드 형태로 존재하며, 자체적인 간단한 CPU와 메모리를 가질 수 있음

- 데이터 형식 변환, 장치 제어 등 수행

- 버스를 통해 CPU 및 주기억장치와 통신

- 메모리 매핑 I/O (Memory-Mapped I/O):

- 입출력 장치의 제어 레지스터나 데이터 버퍼를 메모리 주소 공간의 일부처럼 할당

- CPU는 일반적인 메모리 접근 명령어(LOAD, STORE)를 사용하여 입출력 장치와 통신 가능

직접 메모리 접근 (DMA - Direct Memory Access)

- 제어기가 CPU의 개입 없이 직접 주기억장치에 접근하여 데이터를 전송하는 기능

- 대량의 데이터를 전송할 때(예: 하드 디스크) CPU의 부담을 줄여 시스템 효율성 향상

- CPU와 DMA 제어기가 동시에 버스 사용을 시도하면 버스 경합(Bus Contention) 또는 버스 정체 현상 발생 가능 (폰 노이만 병목 현상의 일부)

핸드셰이킹 (Handshaking)

- 두 장치 간 데이터 전송 시, 서로 제어 신호를 주고받으며 전송 상태를 확인하고 동기화하는 과정

- 데이터 전송의 신뢰성 보장

- 예: 송신측이 데이터 준비 완료 신호 전송 → 수신측이 수신 준비 완료 신호 전송 → 데이터 전송 → 수신측이 수신 완료 신호 전송

신호 전달 방식 (Signal Transmission Methods)

- 병렬 전송 (Parallel Transmission):

- 여러 비트를 동시에 여러 개의 선(회선)을 통해 전송

- 속도가 빠르지만 거리가 길어지면 신호 간 간섭 문제 발생 가능

- 예: 컴퓨터 내부 버스, 구형 프린터 포트 (IEEE 1284)

- 직렬 전송 (Serial Transmission):

- 비트를 한 번에 하나씩 순서대로 하나의 선을 통해 전송

- 전송 거리가 길어도 비교적 안정적, 클럭 속도를 높여 고속 전송 가능

- 예: USB, RS-232, 이더넷, PCI Express

다양한 통신 매체 및 기술

- 광섬유 전송 (Optical Fiber Transmission):

- 빛 신호를 이용하여 데이터를 전송하는 방식

- 매우 높은 대역폭, 낮은 신호 감쇠, 긴 전송 거리, 전자기 간섭에 강함

- 인터넷 백본망 등에 주로 사용

- 무선 전송 (Wireless Transmission):

- 전자기파(라디오파, 마이크로파 등)를 이용하여 데이터를 전송

- 이동성과 편리성 제공

- 환경(장애물, 거리, 다른 신호 간섭)에 따라 신호 품질 영향 받음

- 예: WiFi, Bluetooth, LTE, 5G

- DSL (Digital Subscriber Line):

- 기존 전화선을 이용하여 디지털 데이터를 고속으로 전송하는 기술

- ADSL(비대칭), VDSL(초고속) 등 다양한 표준 존재

- 케이블 모뎀 전송 (Cable Modem Transmission):

- 케이블 TV(CATV) 망을 이용하여 데이터를 전송하는 방식

- 고속 인터넷 서비스 제공에 널리 사용됨

통신 속도 (Communication Speed)

- 대역폭 (Bandwidth): 통신 경로를 통해 단위 시간당 전송될 수 있는 최대 비트 수 (bps - bits per second)

- 높은 대역폭은 단순히 속도가 빠르다는 의미 외에, 동시에 많은 양의 데이터를 전송할 수 있는 용량을 의미

⚠️

bps (bits per second)와 Bps (Bytes per second)를 혼동하지 않도록 주의 (1 Byte = 8 bits)

기타 CPU 구조

파이프라이닝 (Pipelining)

- 하나의 명령어를 처리하는 과정을 여러 단계(예: 인출, 해석, 실행)로 나누어, 각 단계가 동시에 다른 명령어의 부분을 처리하도록 하는 기술

- 기계 주기의 단계들을 중첩시켜 전체 처리율(Throughput, 단위 시간당 처리 작업량)을 높임

- 이상적인 성능 향상을 위한 조건:

- 각 파이프라인 단계의 처리 시간이 균등해야 함

- 파이프라인은 항상 같은 종류의 작업만 처리해야 함

- 파이프라인에 투입되는 작업들은 서로 의존 관계가 없어야 함

- 파이프라인 유지 비용(단계 분할 및 제어) 최소화

슈퍼스칼라 (Superscalar)

- CPU 내부에 여러 개의 파이프라인을 두어, 매 클럭 사이클마다 여러 개의 명령어를 동시에 인출, 해석, 실행할 수 있는 구조

- Intel Nehalem 아키텍처는 4-와이드 슈퍼스칼라 구조 (동시에 4개 명령어 처리 가능)

다중 코어 (Multi-core) 및 병렬 처리 (Parallel Processing)

- 다중 코어: 하나의 CPU 칩 안에 여러 개의 독립적인 처리 장치(코어)를 집적한 구조

- 각 코어는 자체적으로 명령어를 처리하며, 데이터를 공유(L3 캐시, 메모리)하고 협력하여 작업 수행해서 큰 문제를 더 빠르게 해결 가능

- 병렬 처리 분류:

- SISD (Single Instruction, Single Data): 고전적인 단일 프로세서 구조 (하나의 명령, 하나의 데이터)

- SIMD (Single Instruction, Multiple Data): 여러 처리 장치가 동일한 명령을 서로 다른 데이터에 대해 동시에 수행 (벡터 프로세서, GPU 그래픽 처리 일부)

- MISD (Multiple Instruction, Single Data): 여러 명령이 하나의 데이터 스트림에 대해 수행 (실제 구현 사례 거의 없음)

- MIMD (Multiple Instruction, Multiple Data): 여러 처리 장치가 각자 다른 명령을 다른 데이터에 대해 독립적으로 수행 (다중 코어 프로세서, 클러스터)

레퍼런스

“이 글은 『컴퓨터 과학 총론』(Brookshear & Brylow, 2019)의 내용을 토대로 재구성된 자료입니다.”

ƎXCLUSIVE ARCHITECTURE

💻 이 글은 컴퓨터시스템개론 시리즈의 일부입니다.

← 이전글: 데이터의 저장 | 다음글: 운영체제 →